# **Crytalline silicon cell and module construction and technology**

## Crystalline silicon solar cell and modules

## New construction principles

#### PEARL structure (1994)

*microelectronics technology with several photolithographic processes*

- antireflection coating improvement

- high contact quality

- high quality starting (FZ) Si

- minimising the structure thickness

principles of construction and technology were simplified for mass production

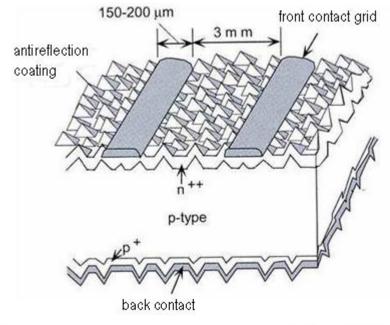

## **Present construction used in mass production**

-Surface texturing without photolithography

- etching monocrystalline (1,0,0) Si in KOH

- acid etching in the case of other crystallographic orientation of Si

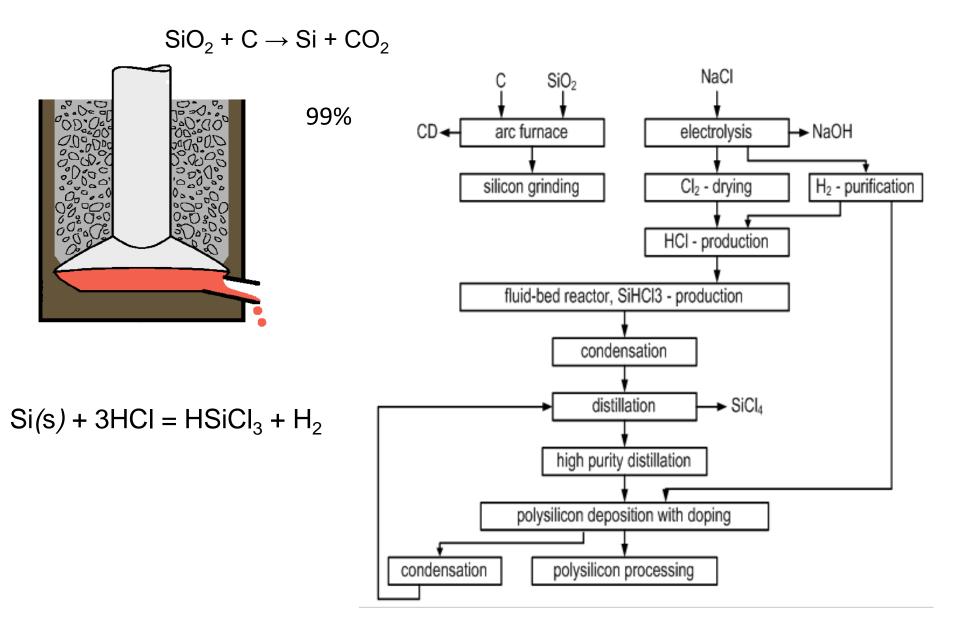

# **Preparing semicondutor silicon**

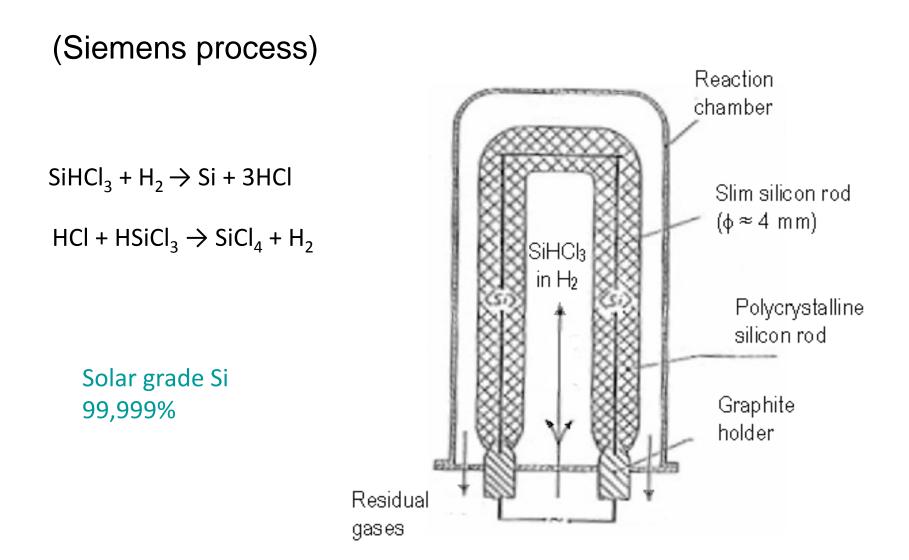

## **Polycrystalline silicon fabrication**

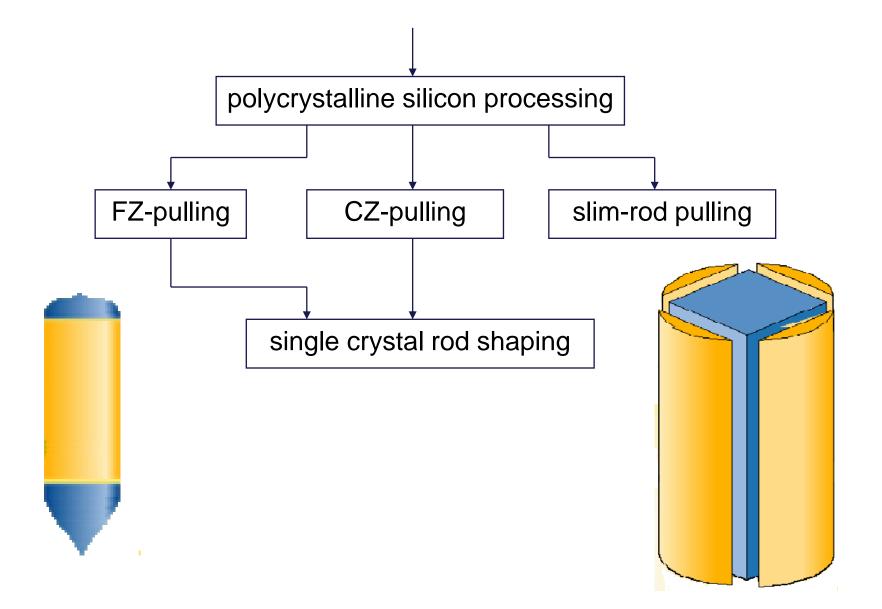

## **Single-crystal fabrication**

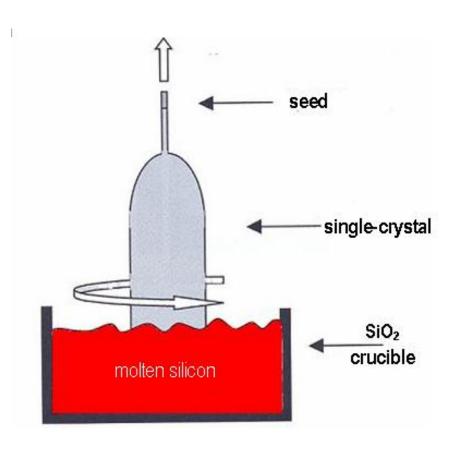

#### Czochralski method

- Diameter up to 450 mm

- Weight up to 300 kg

# **Single-crystal fabrication**

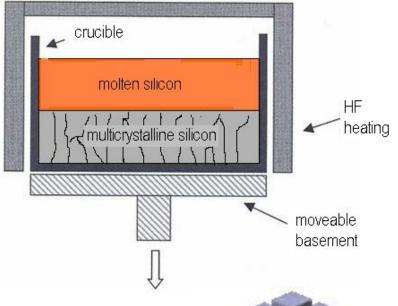

# Multicrystalline rod fabrication

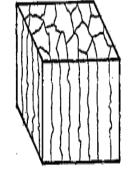

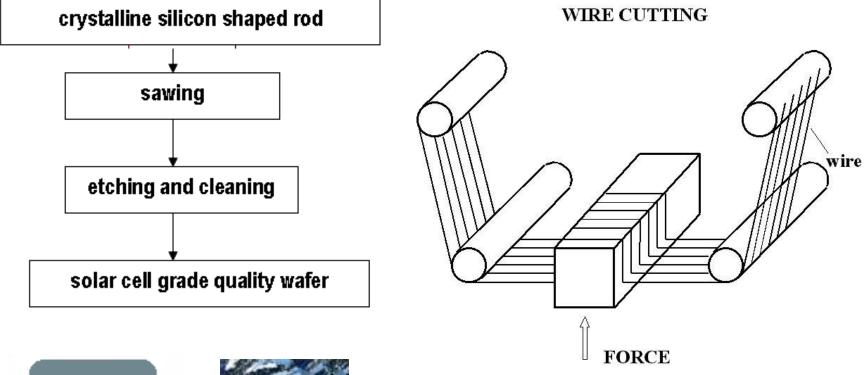

# Wafer fabrication

~40% of material is lost during crystalline rod cutting (sawing)

# Fabrication of c-Si solar cells

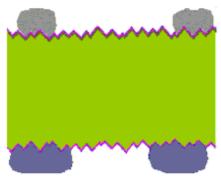

a) Starting silicon wafer, wire cut, without grinding (crystal orientation 1,0,0, P-type)

d) Silicon wafer after one-side phosphorous difussion, diffusion depth about 0.5 μm

g) Print-screening Ag paste on front surface of the cell (a layer about 30-50 µm thick)

b) Silicon wafer after isotropic etching, surface damaged layer (about 30 μm) etched-off

Antireflection coating with silicon nitride layer of thickness about 75 μm, both sides

h) Contact sintering at temperature about 800°C, realisation ohmic contacts, edge grinding.

c) Silicon wafer after surface texturing by anisotropic etching in KOH (NaOH)

f) Print-screening AI + Ag paste on back surface of the cell (a layer 30-50 µm thick)

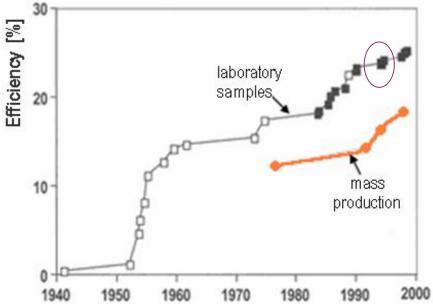

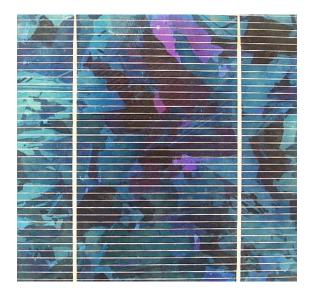

# Crystalline Si solar cells

## mono-crystalline

#### multi-crystalline

$$\eta \leq 17\%$$

$\eta \leq 16\%$

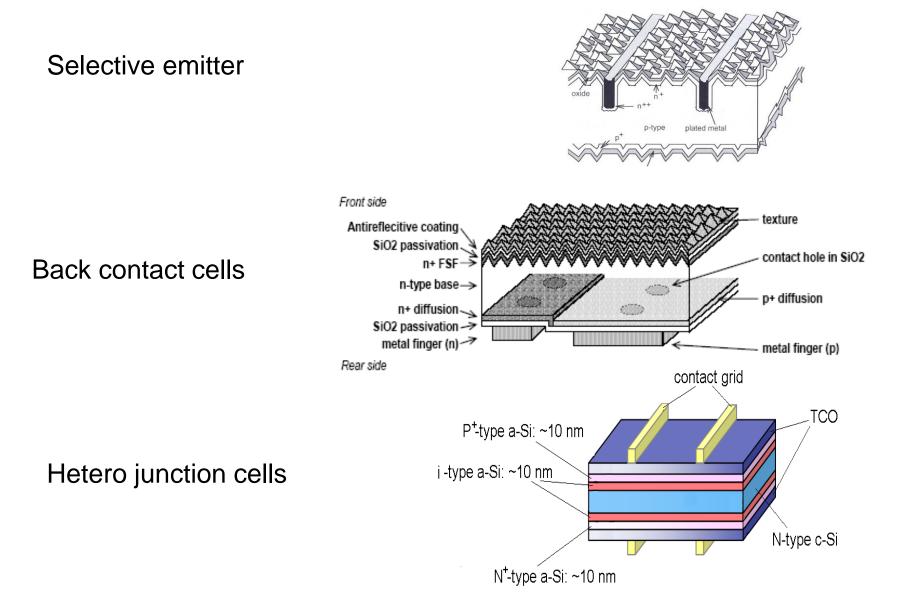

## **Increasing cell efficiency**

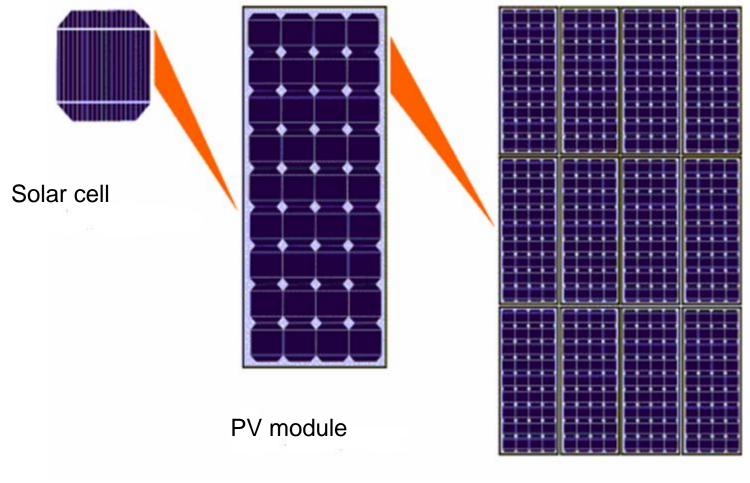

## A single solar cell.....~0.5 V, about 30 mA/cm<sup>2</sup>

For practical use it is necessary connect cells in series to obtain a source of higher voltage and in parallel to obtain a higher current

PV field

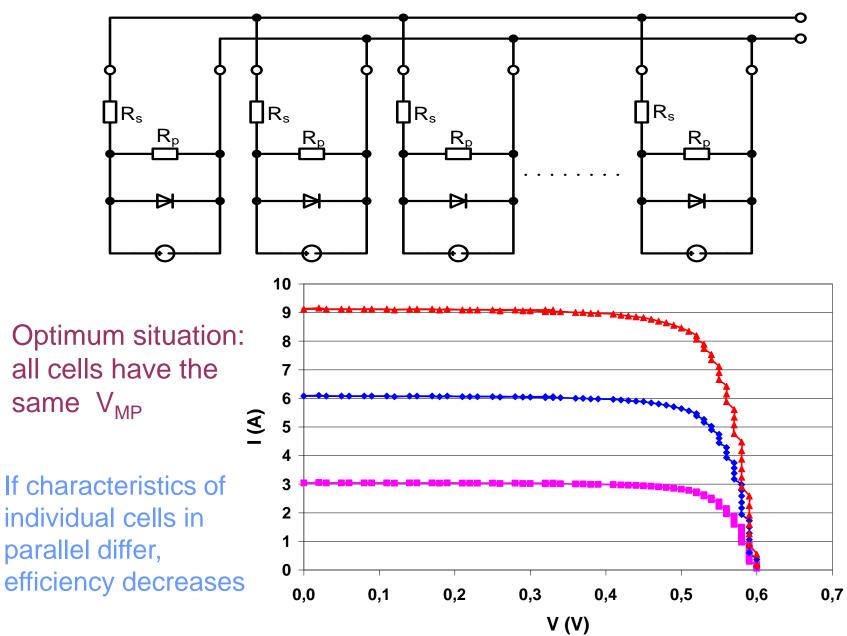

## **Cell connection in parallel**

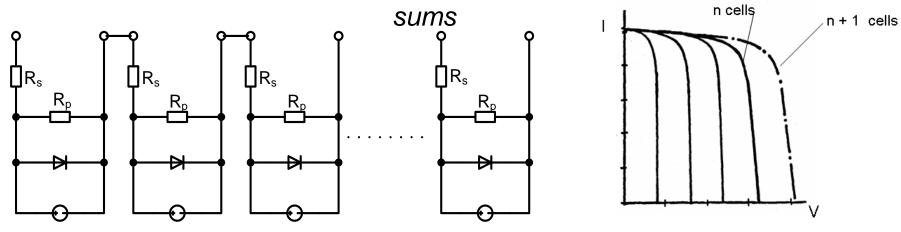

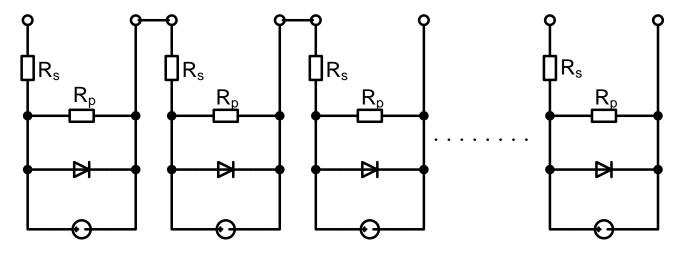

## Cells in series

Cells in series...the same current flows through all cells voltage does

Optimum situation: all cells have the same  $I_{MP}$

If characteristics of individual cells in series differ, efficiency decreases

$$I = I_{PV} - I_{01} \left[ \exp\left(q \frac{V + R_{s}I}{mn_{1}kT}\right) - 1 \right] - I_{02} \left[ \exp\left(q \frac{V + R_{s}I}{mn_{2}kT}\right) - 1 \right] - \frac{V + R_{s}I}{R_{sh}}$$

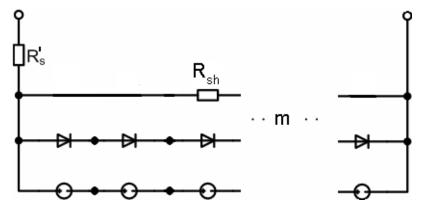

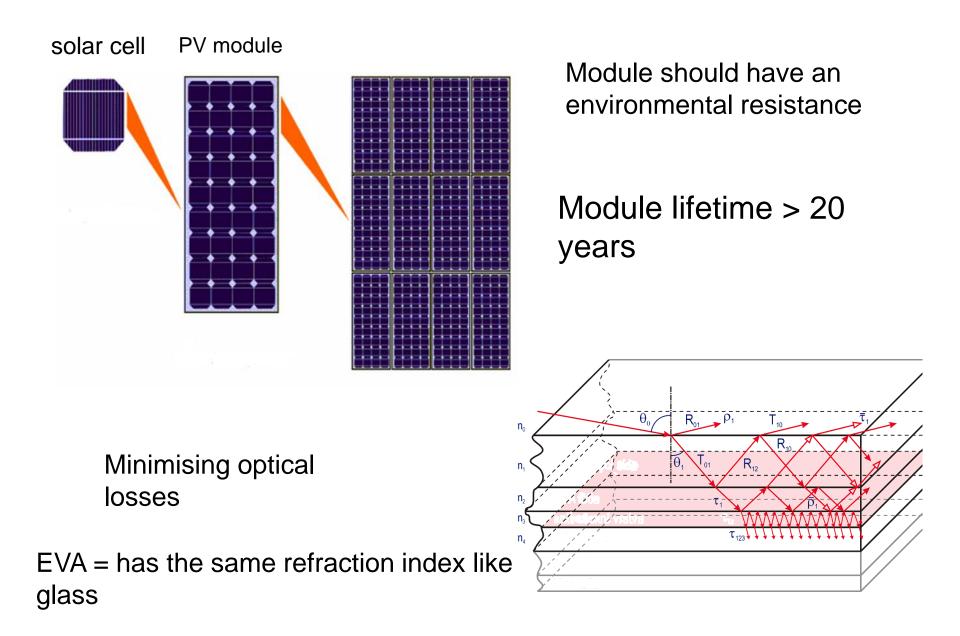

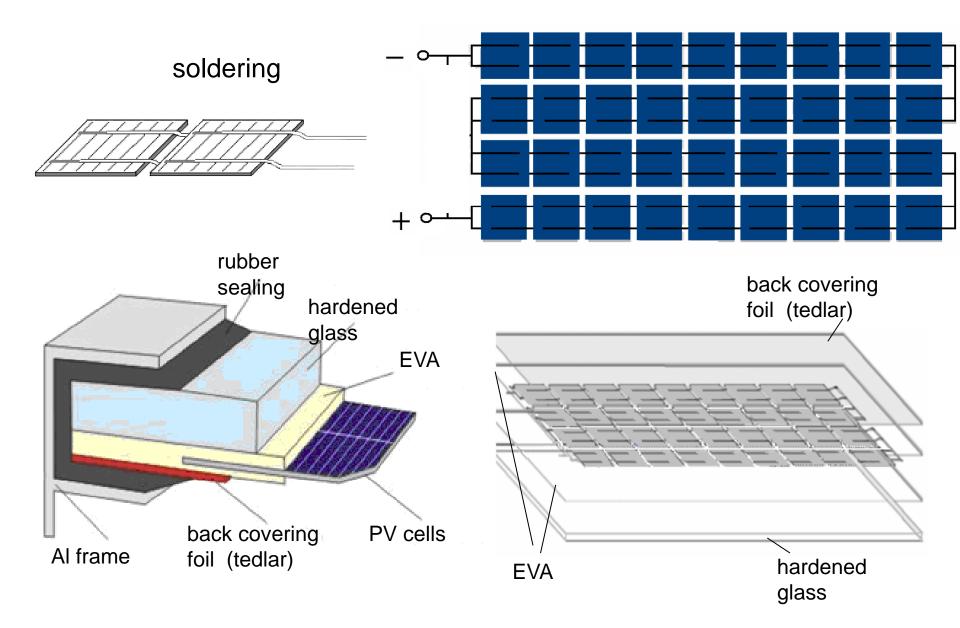

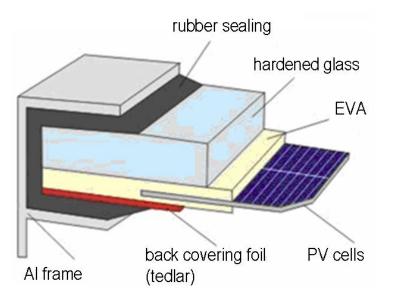

# **PV module technology**

# PV c-Si module technology

# **Operating cell temperature**

Operating temperature of cells in the module depends on the ambient temperature and the module construction (thermal resistance  $R_{th}$ ).

**NOCT** (Nominal Operating Cell Temperature) is the cell temperature  $T_c$ at the ambient temperature  $T_a' = 20^{\circ}$ C, irradiance G = 0.8 kWm<sup>-2</sup> and the wind speed 1 ms<sup>-1</sup>.

If the module temperature  $T_{mod}$  is measured at the back module surface

$$T_c = T_{\rm mod} + \Delta T \, \frac{G}{G_{SCT}}$$

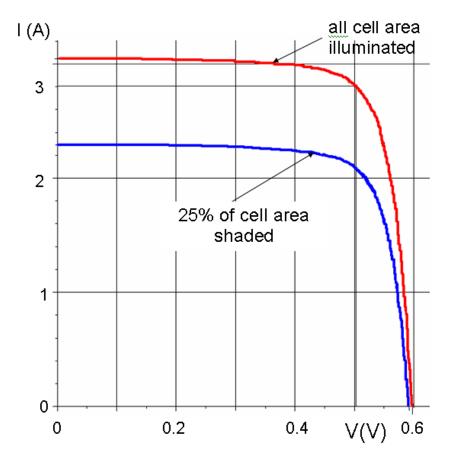

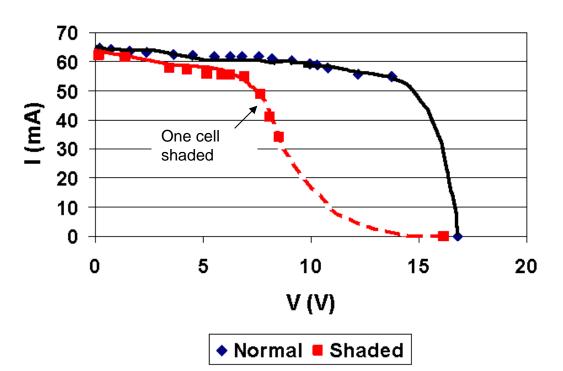

# **Effect of partial shading** – one cell (a decrease of illuminated area A<sub>ill</sub>)

$$I = A_{ill}J_{PV} - I_{01}\left[\exp\left(q\frac{V+R_sI}{kT}\right) - 1\right] - I_{02}\left[\exp\left(q\frac{V+R_sI}{2kT}\right) - 1\right] - \frac{V+R_sI}{R_p}$$

$$V_{OC} = \frac{2kT}{q} \ln \left( \frac{-I_{02} + \sqrt{I_{02}^{2} + 4I_{01}(I_{02} + I_{01} + A_{ill}J_{PV})}}{2I_{01}} \right)$$

In the case of one cell

- a decrease of the output current (proportional to area illuminated)

- a decrease of the output voltage

- a decrease of the output power

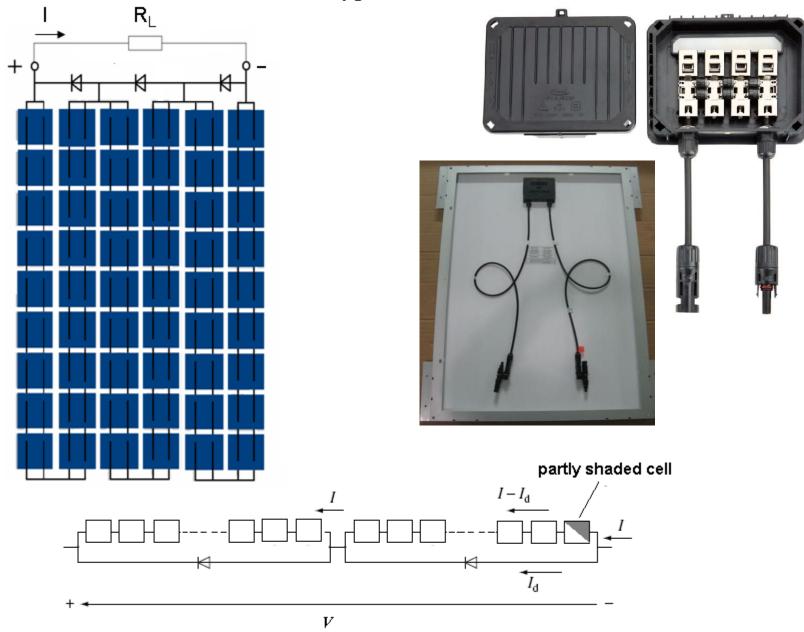

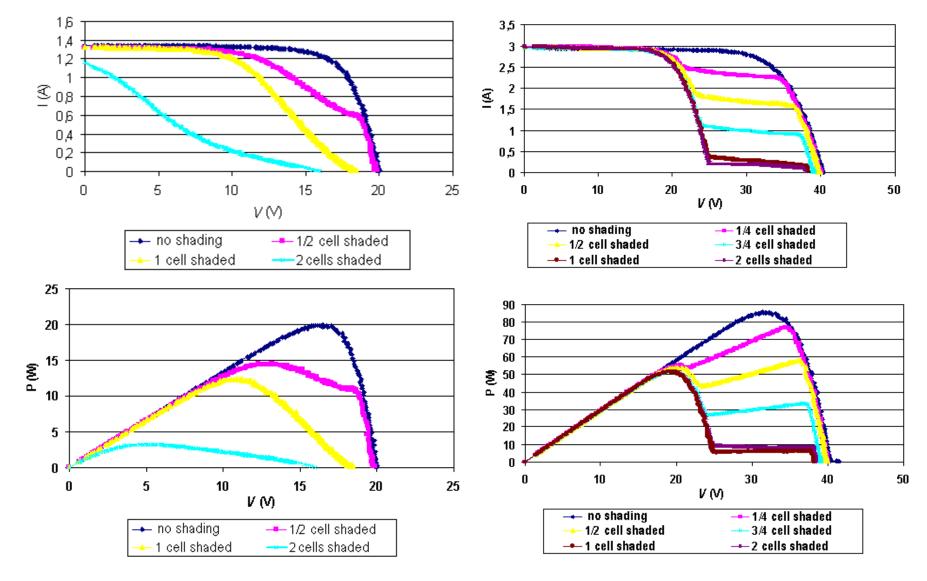

## Effect of partial shading – cells in series

In the case of cells in series increases series resistance

- a decrease of the output current

- a decrease of the output voltage

- a considerable decrease of the output power

## Bypass diodes

## Vliv překlenovacích diod

#### Without diodes

#### With bypass diodes

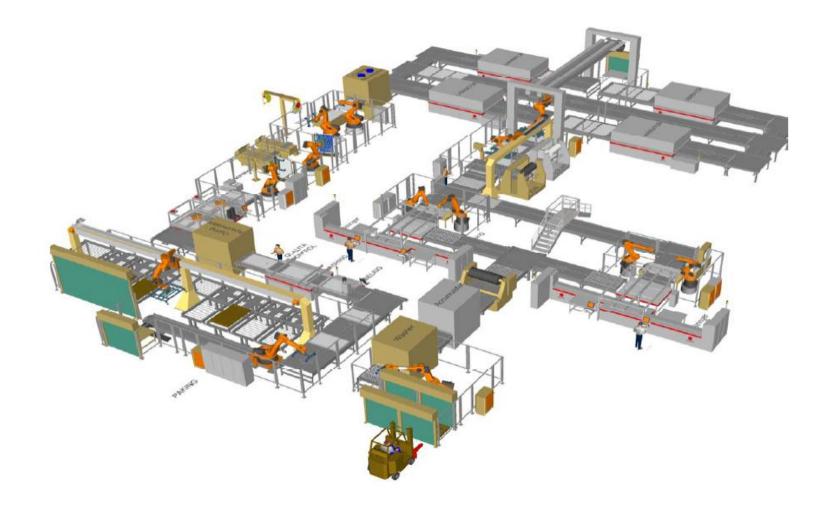

In 2012 about 28  $GW_p$  of c-Si modules were installed (90% of total) The installed modules have area about 225 km<sup>2</sup>